# RADIATION ANALYSIS AND DESIGN TOOLS

#### JRC's Analysis and Simulation Tools

JRC's Robust Chip Platform is the industry's leading provider of analysis and simulation tools for soft errors and radiation effects. JRC's analysis and simulation tools include accurate Soft Error Rates (SER) and latchup prediction, layout and circuit optimization, chip SER prediction, and more.

Harnessing cutting-edge techniques, our Radiation Analysis and Design Software provides unmatched accuracy in analyzing radiation error rates for standard cell libraries. These advanced tools empower semiconductor designers to create reliable, mission-critical solutions with precision.

JRC's Robust Chip tool suite contains complete circuit simulation and unique 2D/3D device simulation (Accuro, rExplore and Roplace) with specialized models for single event effects and latchup. The tools provide complete and accurate SER and latchup rates and fully support layout and circuit optimization for single event effects. Our novel technology for logic analysis (Relience) ties the cell and circuit analysis to full chip level analysis.

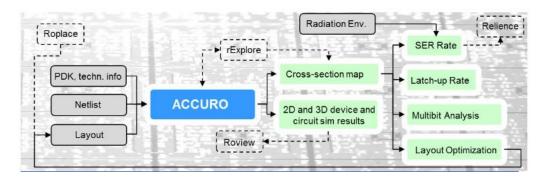

#### Accuro

#### Device and circuit simulation with fast single event analysis.

Accuro contains complete 2D and 3D device simulation and complete (spice-type) circuit simulation. Using a unique, fast, simulation mode for single event analysis, it is capable of generating exhaustive single event analysis (full cross-section maps), with full layout dependence, for layouts containing 100ds of devices.

Accuro has a very wide range of capabilities and is widely applied in the industry.

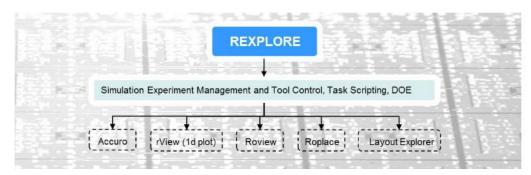

## **Rexplore**

#### Management of simulation experiments and results evaluation.

rExplore is a management tool for simulation experiments. It supports the design and set-up of simulation experiments, the execution (including job distribution), and the post-simulation extraction and analysis. The capabilities of rExplore can be customized using tasks and task-scripts.

rExplore and Accuro are widely used in the industry to calculate single event cross-sections and to predict single event error rates for different radiation environments.

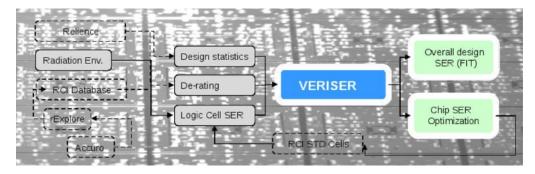

## **Veriser**

#### SER prediction for large logic designs.

Veriser is part of an existing new technology from JRC, which ties the analysis of single event effects for logic cells, and for smaller circuits, to the prediction and analysis of overall SER rates for very large logic designs.

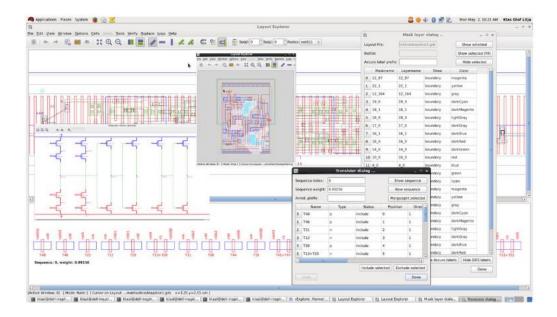

## **Layout Explorer**

#### Layout, schematic, and cross-section map visualization.

Layout Explorer is JRC's layout and schematic visualization tool. It also supports visualization of cross-section maps (both in 2D and 3D), extracted net and device information, and device and contact placement information from Roplace.

Layout Explorer can read both the gds and OA layout formats, and the spice, hspice, and spectre netlist formats. The tool can be customized using scripts (in a manner like the task-script in rExplore).

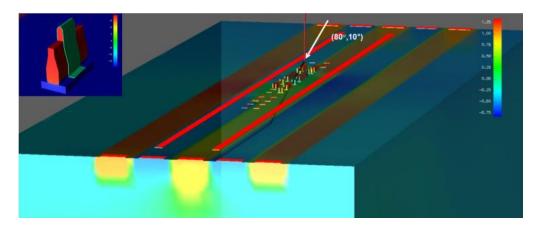

## **Roview**

#### 2D AND 3D Visualization.

Roview is used to visualize all aspects of the 2D and 3D structures, data from Accuro, and certain aspects of cross-section maps, such as the spherical plot showing cross-section, or error rate, as a function of the incoming angle of the ionizing particle.

Roview is a state-of-the art visualization tool based on a customized version of DataExplorer.

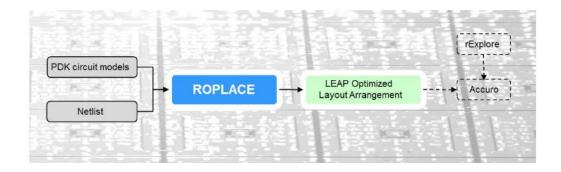

# **Roplace**

## Automated, LEAP-based layout optimization.

Roplace is an optimization tool that automates the LEAP methodology. The tool applies LEAP design rules, user constraints, and single event circuit simulation to optimizes the ordering of devices and contact areas in the layout for minimal SER sensitivity.

Roplace provides guidance for the layout optimization but does not provide completed layouts.